- 您现在的位置:买卖IC网 > Sheet目录3881 > PIC18LF8585T-I/PT (Microchip Technology)IC PIC MCU FLASH 24KX16 80TQFP

PIC18F6585/8585/6680/8680

DS30491C-page 112

2004 Microchip Technology Inc.

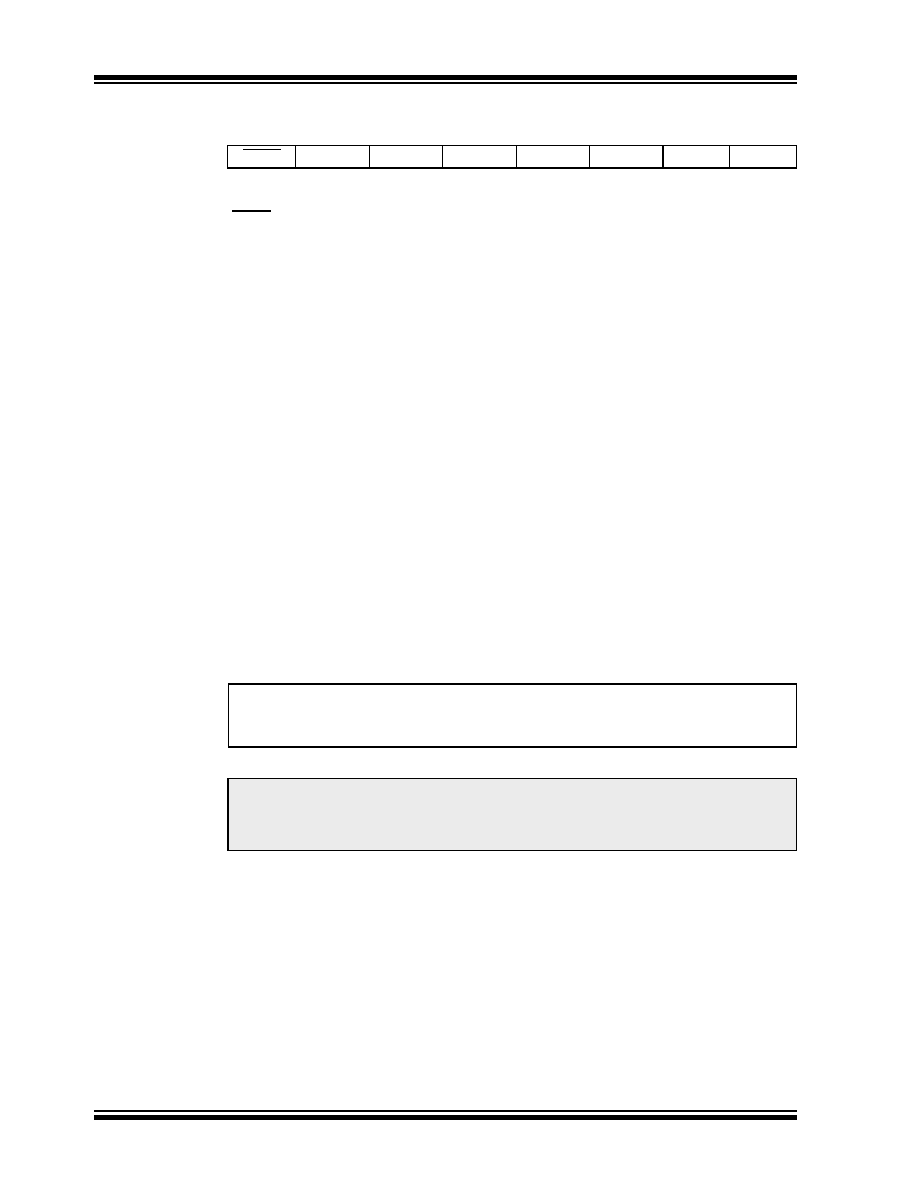

REGISTER 9-2:

INTCON2 REGISTER

R/W-1

RBPU

INTEDG0

INTEDG1

INTEDG2

INTEDG3

TMR0IP

INT3IP

RBIP

bit 7

bit 0

bit 7

RBPU: PORTB Pull-up Enable bit

1

= All PORTB pull-ups are disabled

0

= PORTB pull-ups are enabled by individual port latch values

bit 6

INTEDG0: External Interrupt 0 Edge Select bit

1

= Interrupt on rising edge

0

= Interrupt on falling edge

bit 5

INTEDG1: External Interrupt 1 Edge Select bit

1

= Interrupt on rising edge

0

= Interrupt on falling edge

bit 4

INTEDG2: External Interrupt 2 Edge Select bit

1

= Interrupt on rising edge

0

= Interrupt on falling edge

bit 3

INTEDG3: External Interrupt 3 Edge Select bit

1

= Interrupt on rising edge

0

= Interrupt on falling edge

bit 2

TMR0IP: TMR0 Overflow Interrupt Priority bit

1

= High priority

0

= Low priority

bit 1

INT3IP: INT3 External Interrupt Priority bit

1

= High priority

0

= Low priority

bit 0

RBIP: RB Port Change Interrupt Priority bit

1

= High priority

0

= Low priority

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

- n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

Note:

Interrupt flag bits are set when an interrupt condition occurs regardless of the state

of its corresponding enable bit or the global enable bit. User software should ensure

the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature

allows for software polling.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XF2J-3024-11

CONN FPC 30POS 0.5MM SMT

PIC18LF6525T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18LF8621T-I/PT

IC PIC MCU FLASH 32KX16 80TQFP

PIC18F8620T-E/PT

IC PIC MCU FLASH 32KX16 80TQFP

PIC18F8720T-E/PT

IC PIC MCU FLASH 64KX16 80TQFP

PIC18F4439T-E/ML

IC PIC MCU FLASH 6KX16 44QFN

XF2J-2824-11

CONN FPC 28POS 0.5MM SMT

PIC18F4439T-E/PT

IC PIC MCU FLASH 6KX16 44TQFP

相关代理商/技术参数

PIC18LF8620-I/PT

功能描述:8位微控制器 -MCU 64KB 3840 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18LF8620-I/PT

制造商:Microchip Technology Inc 功能描述:8BIT FLASH MCU 18LF8620 TQFP80

PIC18LF8620-I/PTC01

制造商:Microchip Technology Inc 功能描述:

PIC18LF8620T-I/PT

功能描述:8位微控制器 -MCU 64KB 3840 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18LF8621-I/PT

功能描述:8位微控制器 -MCU 64KB 3840 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18LF8621T-I/PT

功能描述:8位微控制器 -MCU 64KB 3840 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18LF8622-I/PT

功能描述:8位微控制器 -MCU 64 KB FL 4K RAM 70 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18LF8622T-I/PT

功能描述:8位微控制器 -MCU 64 KB FL 4K RAM 70 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT